目录标题1、实验目的2、实验设备3、实验内容4、实验原理5.新建工程:6.顶层设计:7.时钟设计:8. 添加控件:9. 完成后续:10.继续设计顶层:1、实验目的(1)学习 Quartus Prime 、Platform Designer、Nios II SB...

目录标题

- 1、实验目的

- 2、实验设备

- 3、实验内容

- 4、实验原理

- 5.新建工程:

- 6.顶层设计:

- 7.时钟设计:

- 8. 添加控件:

- 9. 完成后续:

- 10.继续设计顶层:

1、实验目的

(1)学习 Quartus Prime 、Platform Designer、Nios II SBT 的基本操作;

(2)初步了解 SOPC 的开发流程,基本掌握 Nios II 软核的定制方法;

(3)掌握 Nios II 软件的开发流程,软件的基本调式方法。

2、实验设备

硬件:PC 机、DE2-115 FPGA 实验开发平台;

软件:Quartus Prime 18.1、Platform Designer、Nios II SBT

3、实验内容

使用 FPGA 资源搭建一个简单 Nios II 处理器系统,具体包括:

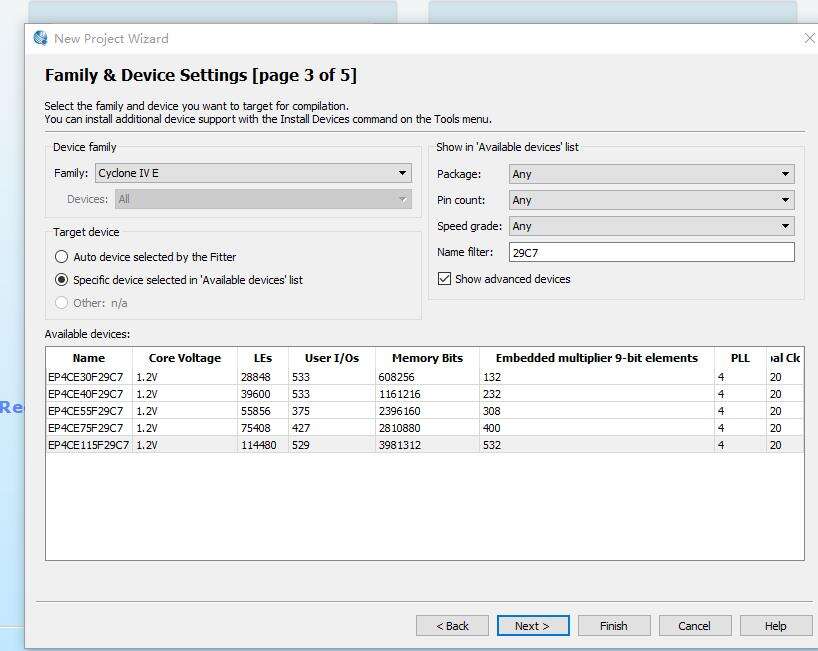

(1) 在 Quartus Prime 中建立一个工程;

(2) 使用 PD 建立并生成一个简单的基于 Nios II 的硬件系统;

(3) 在 Quartus Prime 工程中编译基于 Nios II 的硬件系统并生成配置文件.sof;

(4) 在 Nios II SBT 中建立对应硬件系统的用户 C/C++工程,编写一简单用户程序,在

Nios II SBT 中编译程序生成可执行文件.elf;

(5) 将配置文件.sof 和可执行文件.elf 都下载到 FPGA 进行调试运行。

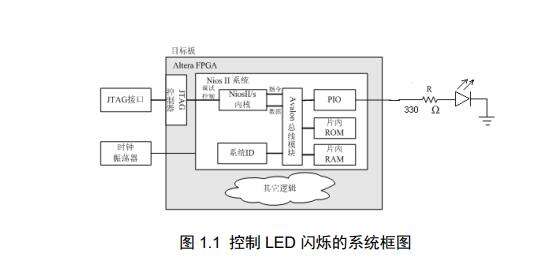

4、实验原理

控制 LED 灯闪烁的用户程序代码很小,可将其固化在片内 ROM 来执行。变量、堆栈

等空间使用片内 RAM,不使用任何片外存储器。整个系统的框图如图 1 所示。

从图 1.1 控制 LED 闪烁的系统框图可知,其它逻辑与 Nios II 系统一样可存在于 FPGA

中。Nios II 系统可与其它片内逻辑相互作用,取决于整个系统的需要。为了简单起见,本实

验在 FPGA 内不包括其它逻辑。

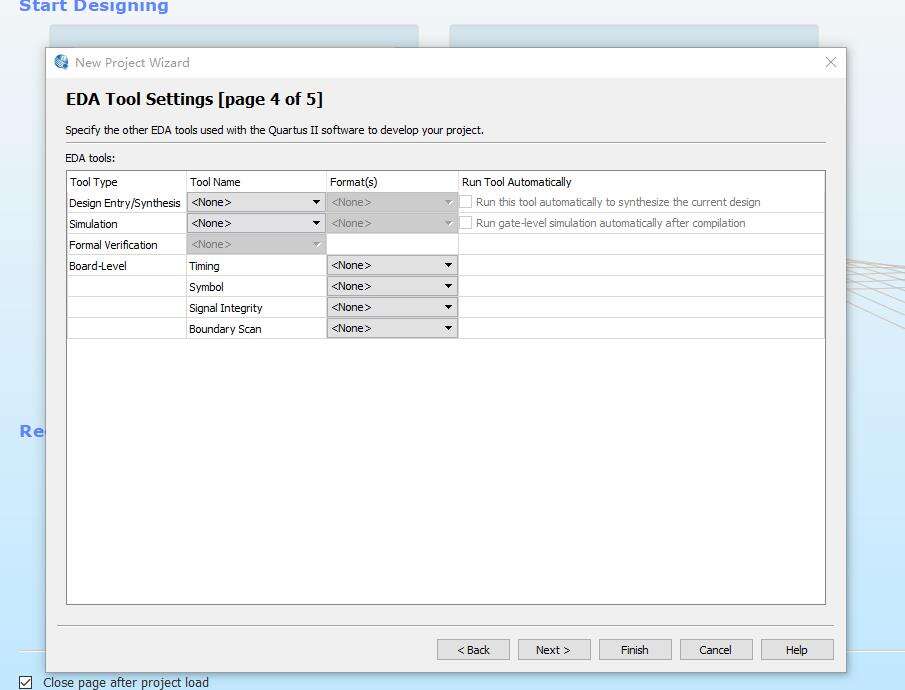

5.新建工程:

(正在做)

6.顶层设计:

7.时钟设计:

8. 添加控件:

9. 完成后续:

10.继续设计顶层:

本文标题为:第八周实验--FPGA的NIOS-II开发入门

- 最好用的ios数据恢复软件:PhoneRescue for Mac 2023-09-14

- iOS 对当前webView进行截屏的方法 2023-03-01

- Flutter实现底部和顶部导航栏 2022-08-31

- Android MaterialButton使用实例详解(告别shape、selector) 2023-06-16

- 详解flutter engine 那些没被释放的东西 2022-12-04

- Android实现监听音量的变化 2023-03-30

- Android studio实现动态背景页面 2023-05-23

- Android实现轮询的三种方式 2023-02-17

- 作为iOS开发,这道面试题你能答出来,说明你基础很OK! 2023-09-14

- SurfaceView播放视频发送弹幕并实现滚动歌词 2023-01-02